芯片:RT1021

SDK: SDK_2.12.0_EVK-MIMXRT1020 (freertos_hello)

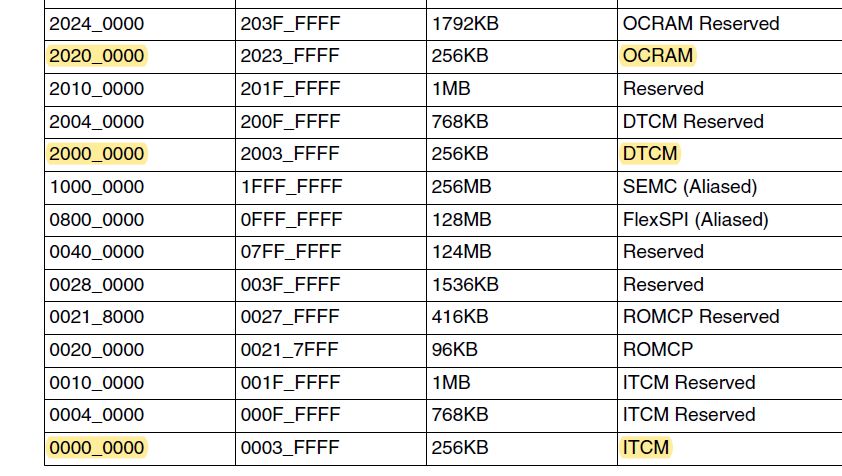

内部RAM:256KB

总RAM = ITCM + DTCM + OCRAM

详细资料:请关注公众号《跳跃的影子》并发送“ RT1021修改内部RAM全为OCRAM ”获取。

修改内部RAM全为OCRAM

- 内部RAM MAP

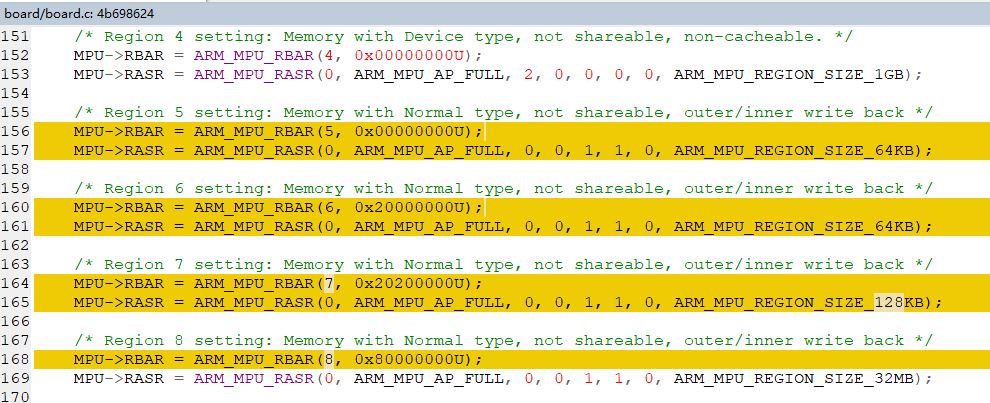

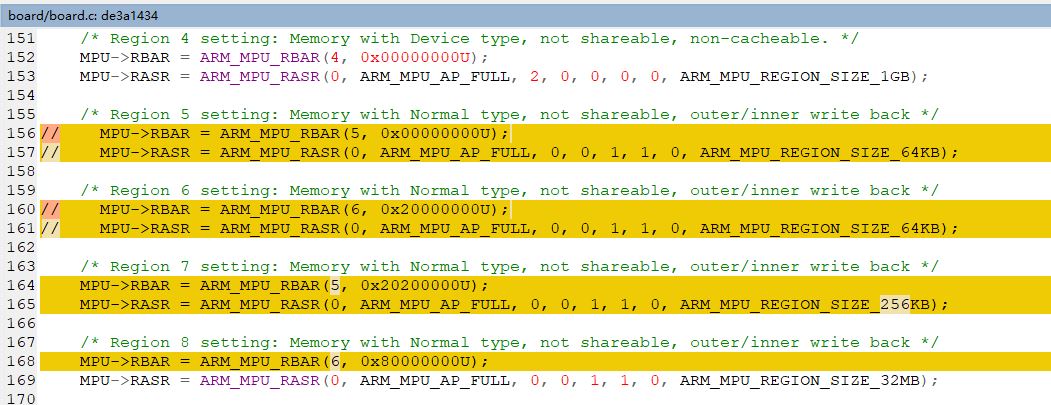

修改MPU

- 从

ITCM和DTCM确定需要屏蔽MPU配置(L156 - L161)。 - 将

OCRAM的128KB扩大到256KB。 - 按顺序修改

ARM_MPU_RBAR第一个参数。

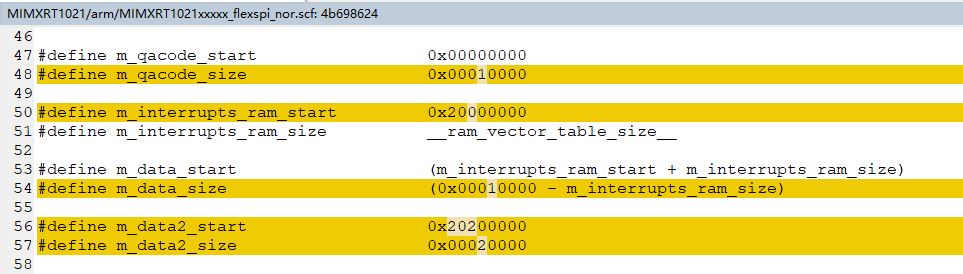

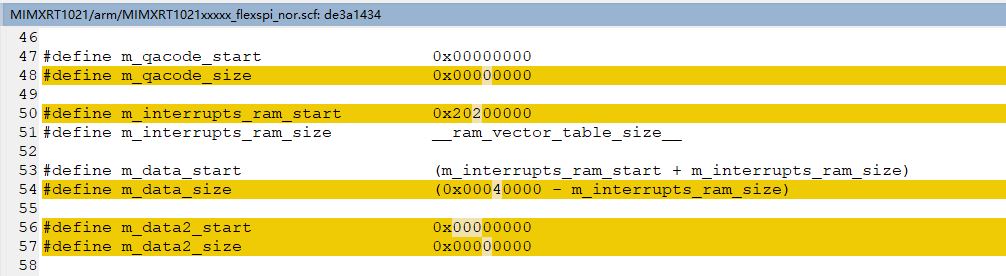

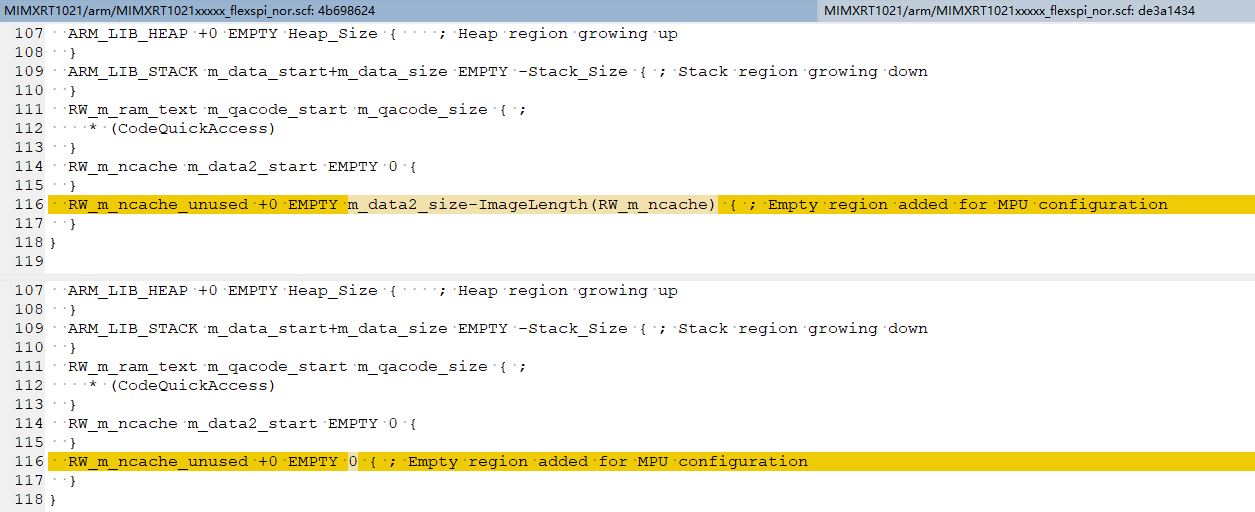

修改分散加载文件

- 将

ITCM和DTCM的地址和大小都改为 0 。- 不建议直接删除,与代码有一定的关联改起来麻烦。

- 将中断地址修改为

OCRAM(0x20200000) 的地址,大小改为0x00040000(256KB) 。

- 将未用的

ncache大小改为 0 。

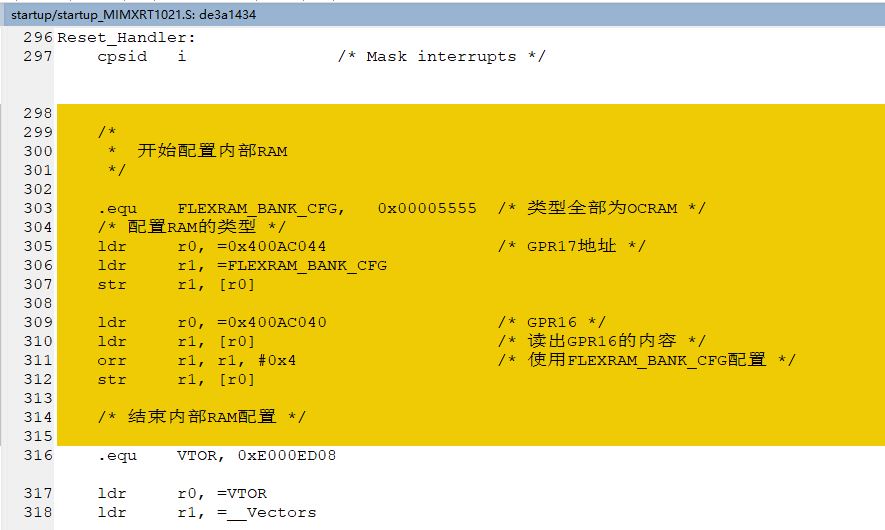

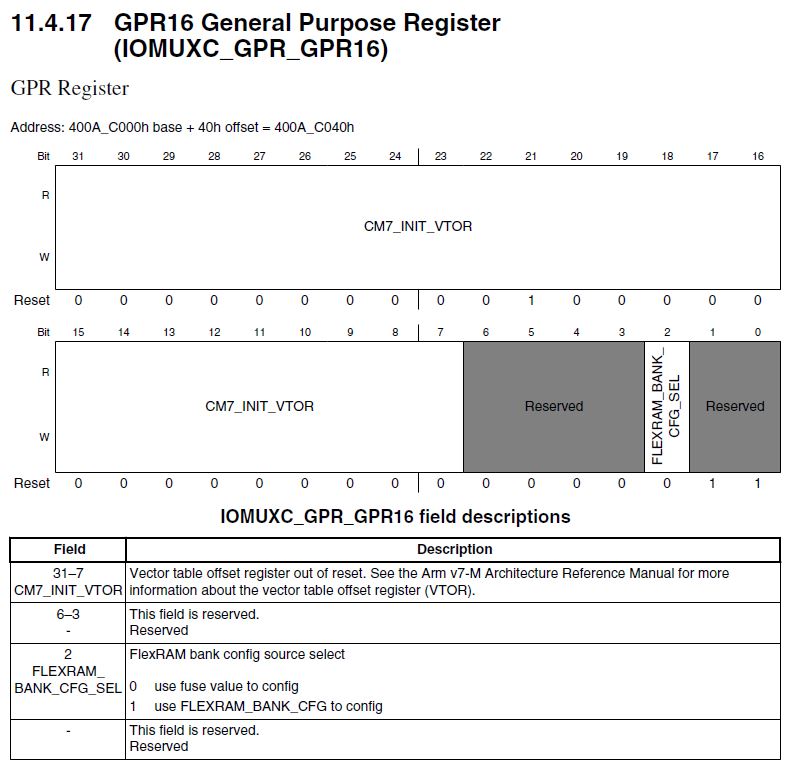

初始化寄存器

- 在

.S文件的Reset_Handler中添加对GPR17和GPR16寄存器的初始化。

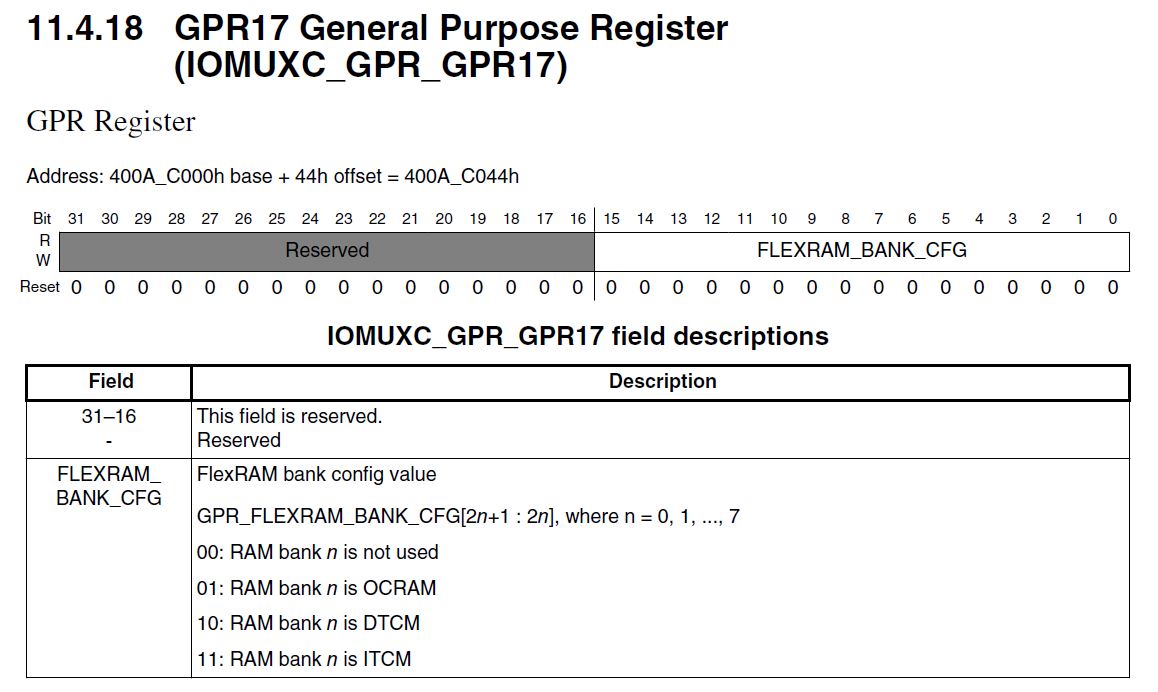

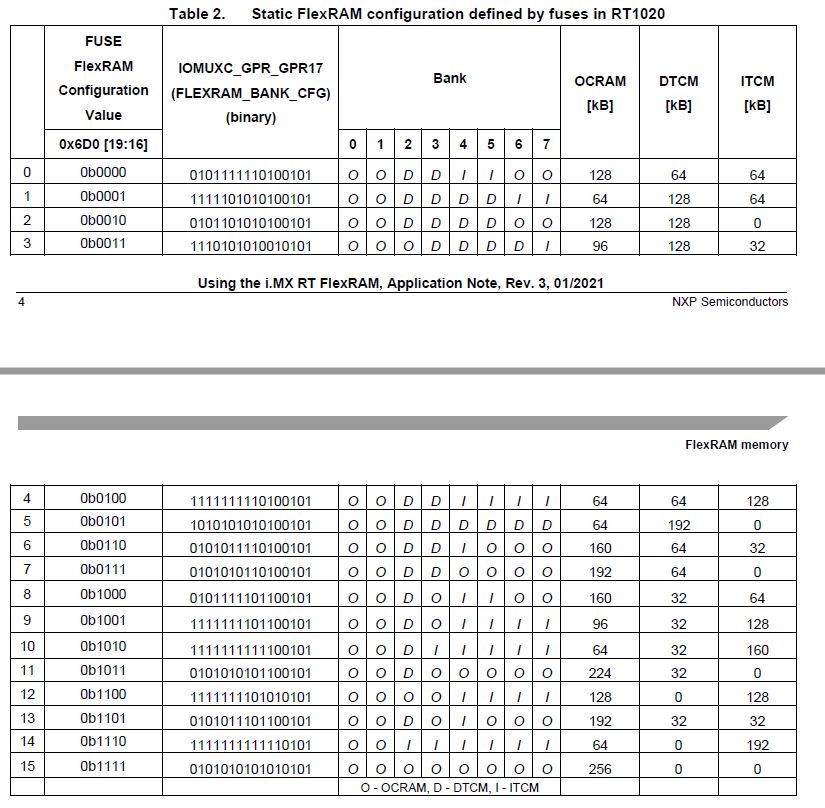

256KB被分为8个区域 (每个区域32KB) ,通过低16位对每一个区域的用途进行配置。

- 将

GPR16的bit2置一使用GPR17的配置取代fuse的默认配置。

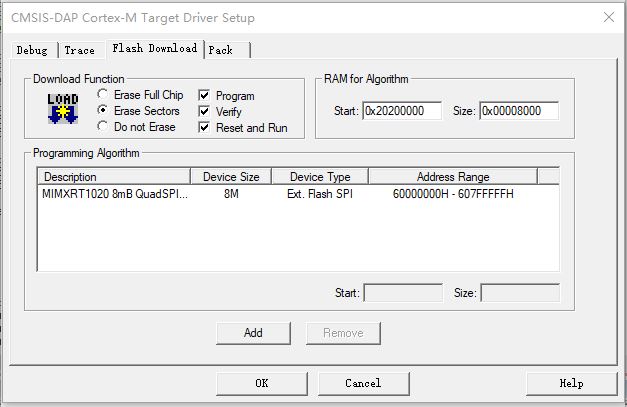

keil配置

keil默认下载算法的地址需要改为OCRAM的地址,否则下载了一次代码后会出现DTCM无法访问的情况。- 在

.S里将所有块配置成了OCRAM,所以DTCM无法使用。

- 在

- 也可以通过跳转

BOOT的方式下载。

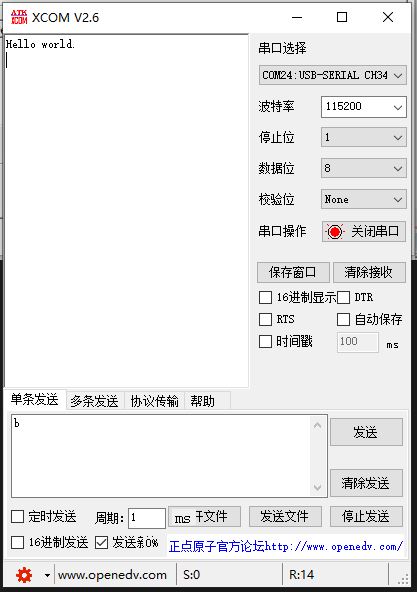

验证

- 串口正常打印。

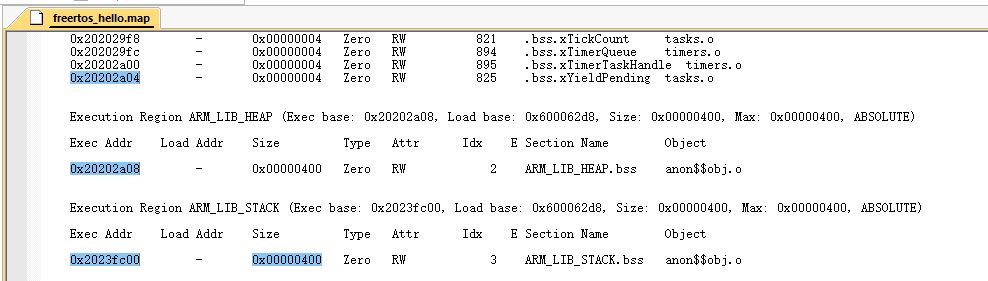

- 查看

.map文件,堆栈分别位于代码结尾和OCRAM结尾。

补充说明

以下说明源于 AN12077 《Using the i.MX RT FlexRAM》

OCRAM通过AXI总线连接,速度要慢于xTCM。约为主频的1/4。

The OCRAM controller is connected through the 64-bit AXI bus to one slave port of the interconnect bus fabric (NIC). This slave port frequency is limited. For example, on RT 1050, if the Arm Cortex-M7 core runs at 528 MHz, then the AXI bus connected to the OCRAM controller is limited to 132 MHz. Expect performance degradation in the data access to the OCRAM in comparison to the xTCM memories. The L1 CACHE memory can help with that.

On RT10xx, the NIC clock ratio of the slave port versus the master port is fixed to 4 (for example, 528 MHz/132 MHz). On RT117x, the ratio depends on master clock and bus clock setting, for example in default it is 1GHz/240MHz

OCRAM最少需要配置为64KB,不能为0。

The minimum configuration of OCRAM is 64 KB (see Table 1). This is required due to ROM code requires at least 64 KB of RAM for its execution. The minimum OCRAM requirements can be device dependent.

- 参考配置表

评论区